# 京都大学大学院情報学研究科 通信情報システムコース 修士課程入学者選抜試験問題 (2023年度10月期入学・2024年度4月期入学)

Admissions for October 2023 and for April 2024

Entrance Examination for Master's Program

Communications and Computer Engineering Course

Graduate School of Informatics, Kyoto University

2023年8月7日 9:00 – 12:00

August 07, 2023 9:00 a.m. - 12:00 noon

# 専門基礎A <u>Problem</u> Set A

### 注意 (NOTES)

- 1. 解答開始の合図があるまで中を見てはいけない。

- 2. これは<u>「専門基礎A」</u>の問題用紙で、表紙共に 9 枚 ある。解答開始の合図があった後、枚数を確かめ、落丁または不鮮明なものがあれば直ちに申し出ること。

- 3. 問題は4問(A-1, A-2, A-3, A-4)ある。<u>4問全てに解答すること。</u>答案用紙の問題番号欄に問題番号を記入すること。

- 4. 解答は問題ごとに答案用紙1枚を使うこと。答案用紙1枚に2問以上の解答もしくは1問の解答を2枚以上の答案用紙に書いた場合は無効にすることがある。なお、必要な場合「裏に続く」と明記した上で 裏面を使用してもよい。

- 5. 答案用紙は4枚綴じたまま使用し、切り離さないこと。

- 6. 答案用紙の綴じ込みがはずれた場合は、直ちに申し出ること。

- 7. 解答は日本語または英語で行うこと。

- 1. Do not open the pages before a call for starting.

- 2. This is the "Problem Set A" in 9 pages including this front cover.

After the call of starting, check all pages are in order and notify proctors (professors) immediately if missing pages or with unclear printings are found.

- 3. There are 4 questions: A-1, A-2, A-3, and A-4. Answer all the questions. State the Question Numbers on your Answer Sheet.

- 4. Use one sheet for each question. If required, the reverse side may be used, stating "Over" at the end of the page. Note that in case two or more questions are answered in one sheet or two or more sheets are used for one question, they may be regarded as no answers.

- 5. Do not separate the pages of answer sheets; keep them bound.

- 6. Notify proctors (professors) immediately if the pages are separated for some reason.

- 7. Answer the questions either in Japanese or English.

Japanese version shall be the authorized version; the English translation for reference only.

## 専門基礎 A

A-1, A-2, A-3, A-4 の4問全てに解答せよ。

### Problem Set A

Answer all questions of A-1, A-2, A-3, and A-4.

## A-1

下記のすべての問に答えよ.

- (1) 下記の問に答えよ. ただし、z = f(x,y),  $x = r\cos\theta$ ,  $y = r\sin\theta$ , r > 0 である.

- (a) 次の式が成り立つことを示せ.

$$\left(\frac{\partial z}{\partial x}\right)^2 + \left(\frac{\partial z}{\partial y}\right)^2 = \left(\frac{\partial z}{\partial r}\right)^2 + \frac{1}{r^2} \left(\frac{\partial z}{\partial \theta}\right)^2$$

(b) 次の式が成り立つことを示せ.

$$\frac{\partial^2 z}{\partial x^2} + \frac{\partial^2 z}{\partial y^2} = \frac{\partial^2 z}{\partial r^2} + \frac{1}{r^2} \cdot \frac{\partial^2 z}{\partial \theta^2} + \frac{1}{r} \cdot \frac{\partial z}{\partial r}$$

(2) 下記の問に答えよ. ただし、関数 B(p,q)は次式で与えられる.

$$B(p,q) = \int_0^1 x^{p-1} (1-x)^{q-1} dx \ (p > 0, \ q > 0)$$

(a) 次の式の値を求めよ.

$$B\left(\frac{1}{2},1\right)$$

(b) 次の式の値を求めよ.

$$B\left(\frac{1}{2},\frac{1}{2}\right)$$

(c) 次の式が成り立つことを示せ.

$$pB(p,q) = (q-1)B(p+1,q-1)$$

$(p>0, q>1)$

(3) 下記の問に答えよ. ただし、行列 A は次式で与えられる.

$$A = \begin{bmatrix} 1 & 2 & 2 \\ 2 & 1 & -2 \\ 2 & -2 & 1 \end{bmatrix}$$

- (a) Aの固有方程式を求めよ.

- (b) Aの固有値を求めよ.

- (c) Aの固有ベクトルをすべて求めよ.

Answer all the following questions.

- (1) Answer the following questions. Note that z = f(x, y),  $x = r \cos \theta$ ,  $y = r \sin \theta$ , r > 0.

- (a) Show that

$$\left(\frac{\partial z}{\partial x}\right)^2 + \left(\frac{\partial z}{\partial y}\right)^2 = \left(\frac{\partial z}{\partial r}\right)^2 + \frac{1}{r^2} \left(\frac{\partial z}{\partial \theta}\right)^2.$$

(b) Show that

$$\frac{\partial^2 z}{\partial x^2} + \frac{\partial^2 z}{\partial y^2} = \frac{\partial^2 z}{\partial r^2} + \frac{1}{r^2} \cdot \frac{\partial^2 z}{\partial \theta^2} + \frac{1}{r} \cdot \frac{\partial z}{\partial r}.$$

(2) Answer the following questions. Note that the function B(p,q) is defined as follows:

$$B(p,q) = \int_0^1 x^{p-1} (1-x)^{q-1} dx \ (p > 0, \ q > 0).$$

(a) Find

$$B\left(\frac{1}{2},1\right)$$

.

(b) Find

$$B\left(\frac{1}{2},\frac{1}{2}\right)$$

.

(c) Show that

$$pB(p,q) = (q-1)B(p+1,q-1) \quad (p>0, q>1).$$

(3) Answer the following questions. Matrix A is given as follows:

$$A = \begin{bmatrix} 1 & 2 & 2 \\ 2 & 1 & -2 \\ 2 & -2 & 1 \end{bmatrix}.$$

- (a) Find the eigen equation of matrix A.

- (b) Find the eigenvalues of matrix A.

- (c) Find all the eigenvectors of matrix A.

下記のすべての問に答えよ。演算子 は論理否定、は論理積、+は論理和、⊕は排他的論理和を表す。

Answer all the following questions. Note that operators  $\overline{\phantom{a}}$ ,  $\cdot$ , +, and  $\oplus$  denote logical negation, logical and, logical or, and exclusive or, respectively.

(1) 以下に示す論理関数 f について、以下の問に答えよ。 Answer the following questions on the logic function f defined below.

$$f = ((\overline{a} + \overline{b} + d) \cdot (\overline{b} + \overline{c} + \overline{d}) \cdot (a + \overline{c} + d)) \oplus (\overline{c} \cdot d + \overline{a} \cdot c \cdot \overline{d})$$

- (a) 論理関数 f の最小積和形表現をすべて求めよ。 Give all minimum sum-of-products expressions of f.

- (b) 3 入力 NAND ゲートのみを用いて、論理関数 f を出力とするゲート数最小の論理回路を示せ。なお、入力として、a、b、c、d およびそれらの否定  $\overline{a}$ 、 $\overline{b}$ 、 $\overline{c}$ 、 $\overline{d}$  が与えられるものとする。

Derive a logic circuit that realizes f with the minimum number of 3-input NAND gates only. Assume a, b, c, d and their complements  $\overline{a}, \overline{b}, \overline{c}, \overline{d}$  are available as inputs.

- (c) 論理関数  $g=a\cdot \bar{b}\cdot d+\bar{a}\cdot b\cdot c\cdot \bar{d}$ 、  $r=(\bar{a}+\bar{b}+c+d)\cdot (\bar{a}+b+c+\bar{d})\cdot (\bar{a}+\bar{b}+\bar{c}+d)$  を考える。  $f=(g+h)\cdot r$  を満足するすべての論理関数 h の中から、積項数が最小でリテラル数が最も少ない積和形論理式を持つ論理関数の最小積和形表現を求めよ。  $f=(g+h)\cdot r$  を満足する論理関数 h が存在しない場合には、存在しないと答えよ。 Assume logic functions  $g=a\cdot \bar{b}\cdot d+\bar{a}\cdot b\cdot c\cdot \bar{d}$  and  $r=(\bar{a}+\bar{b}+c+d)\cdot (\bar{a}+b+c+\bar{d})\cdot (\bar{a}+b+c+d)$ . Among all the logic functions of h that satisfy  $f=(g+h)\cdot r$ , derive a minimum sum-of-products expression of a logic function that has the minimum number of product terms with the minimum number of literals in its minimum sum-of-products form. If there is no logic function h that satisfies  $f=(g+h)\cdot r$ , state that h does not exist.

- (2) 表 1 の可変長符号の復号を行う順序回路を設計したい。この順序回路は、1 ビットの入力xと 3 ビットの出力 $(z_2,z_1,z_0)$ を持つ。可変長符号は左のビットから 1 ビットずつシリアルにxに入力され、符号が認識されるたびに $(z_2,z_1,z_0)$ に対応する固定長符号の各ビットがパラレルに出力される。固定長符号の出力がない時は $(z_2,z_1,z_0)=(0,0,0)$ が出力される。初期状態は、過去にxに 0 も 1 も入力されていない状態とする。以下の間に答えよ。We design a sequential circuit that decodes the variable-length codes defined in Table 1. This sequential circuit has a 1-bit input x and a 3-bit output  $(z_2,z_1,z_0)$ . The variable-length codes are given to input x sequentially from the leftmost bit. Every time a given variable-length code is recognized, the corresponding fix-length code is outputted to  $(z_2,z_1,z_0)$  in parallel. When there is no output of the fixed-length code, the output is  $(z_2,z_1,z_0)=(0,0,0)$ . The initial state

continued on next page 次 頁 へ 続 く is the state where neither 0 nor 1 has been previously inputted to x. Answer the following questions.

表 1 (Table 1)

| 固定長符号 (fixed-length code) | 可変長符号 (variable-length code) |  |

|---------------------------|------------------------------|--|

| 001                       | 0                            |  |

| 010                       | 10                           |  |

| 011                       | 110                          |  |

| 100                       | 1110                         |  |

| 101                       | 1111                         |  |

(a) 可変長符号が認識された次のサイクルに固定長符号が出力される Moore 型順序回路 としてこの順序回路を設計するときの状態遷移図を示せ。

Derive a state transition diagram when we design this sequential circuit as a Moore-type sequential circuit that outputs the fixed-length code in the next cycle after the variable-length code is recognized.

(b) 可変長符号が認識されたら直ちに固定長符号が出力される Mealy 型順序回路として この順序回路を設計するときの状態遷移図を示せ。

Derive a state transition diagram when we design this sequential circuit as a Mealy-type sequential circuit that outputs the fixed-length code immediately after the variable-length code is recognized.

(c) (b) の状態遷移図について、状態数を最小化した状態遷移表と出力表を求めよ。状態 数が最小であることをどのようにして確認したかを説明せよ。

Regarding the state transition diagram derived in (b), show the state transition table and the output table with the minimum number of states. Explain how you verified that the number of states is minimal.

(d) (c) で求めた状態遷移表、出力表に対応する順序回路を、最小数のDフリップフロップを用いて実現する。フリップフロップの入力を与える論理関数と、出力 ( $z_2$ ,  $z_1$ ,  $z_0$ ) の論理関数について、それぞれ最小積和形表現を求めよ。なお、Dフリップフロップの初期値は0であり、入力と出力を表す論理変数をそれぞれd, q とせよ。複数のフリップフロップを用いる場合は添え字で区別せよ。

We implement a sequential circuit corresponding to the state transition table and the output table derived in (c) with the minimum number of D flip-flops. Derive the excitation function(s) of the D flip-flop(s) and the output functions of  $(z_2, z_1, z_0)$  in a minimal sum-of-products form. Here, the initial value of a D flip-flop is 0, and logic variables of the input and the output of a D flip-flop are d and q, respectively. If multiple flip-flops are used, distinguish them by subscripts.

下記のすべての問に答えよ.

Answer all the following questions.

(1)  $S_A$  と  $S_B$  は独立で記憶のない定常情報源であり, $S_A$  は情報源記号 0,1 をそれぞれ 2/3,1/3 の確率で, $S_B$  は 0,1 をそれぞれ 4/5,1/5 の確率で発生させる.以下の問に答えよ.ただし, $\log_2 3 = 1.6$ , $\log_2 5 = 2.3$  とせよ.

$S_A$  and  $S_B$  are independent and stationary memoryless information sources.  $S_A$  generates information symbols 0 and 1 with probabilities 2/3 and 1/3, respectively, while  $S_B$  generates 0 and 1 with probabilities 4/5 and 1/5, respectively. Answer the following questions.  $\log_2 3 = 1.6$  and  $\log_2 5 = 2.3$  may be used.

(a) コンパクト符号の定義を述べよ.

Describe the definition of compact code.

(b)  $S_A$  のエントロピーを算出せよ. Find the value of the entropy of  $S_A$ .

(c)  $S_A$  の 2 次の拡大情報源に対し、2 元ハフマン符号化を施せ、また、そのときの情報源記号 1 つあたりの平均符号長を算出せよ、

Find a binary Huffman code for the second extension of  $S_A$  and the expected codeword length per symbol.

(d) 情報源  $S_X$  は 2 つの状態をもち、状態  $s_A$  では  $S_A$  に従い、状態  $s_B$  では  $S_B$  に従って情報源記号を発生させる。  $S_X$  が 1 を発生させると、その状態が遷移する。  $S_X$  の状態遷移図を描け.

An information source  $S_X$  has two states and generates information symbols by following  $S_A$  and  $S_B$  when its state is  $s_A$  and  $s_B$ , respectively.  $S_X$  transits from a state to the other state when it generates 1. Draw the state diagram of  $S_X$ .

(e) 問 (d) の  $S_X$  の定常分布を求めよ.

Find the stationary distribution of  $S_X$  in Question (d).

(f) 問(d)の Sx のエントロピーを算出せよ.

Find the value of the entropy of  $S_X$  in Question (d).

(2) 通信路符号化に関する以下の間に答えよ、ただし、符号 C を生成多項式が  $G(x) = x^4 + x^3 + x^2 + 1$  である符号長 7 の 2 元巡回符号とする.

Answer the following questions related to channel coding. Let C be the binary cyclic code of length 7 that has a generator polynomial  $G(x) = x^4 + x^3 + x^2 + 1$ .

(a) 符号 C の符号語を全て多項式表現で示せ.

Find all codeword polynomials of C.

(b) 多項式表現  $x^2+1$  の情報ビット列が与えられた場合の符号語を多項式表現で示せ.

Find the codeword polynomial for the message polynomial  $x^2 + 1$ .

(c) G(x) による割り算回路を図示せよ.

Draw a division circuit by G(x).

(d) 符号 C により誤りを検出する方法を説明せよ.

Explain how to detect errors by C.

下記のすべての問に答えよ。

Answer all the following questions.

(1) IEEE 754 二進浮動小数点数と同様の表現を持つ、8 ビット幅の二進浮動小数点形式 FP8 を次のように仮定する。FP8 は MSB から LSB に向かって 1 ビットの符号ビット、3 のゲタばき表現による 3 ビットの指数部、暗黙の 1 を用いる 4 ビットの仮数部から構成される。無限大及び非正規化数の表現も IEEE 754 と同様に定義されているとする。例えば符号が 0、指数部が 7、仮数部が 0 であれば正の無限大を表す。また指数部が 0 であれば非正規化数を表すとする。以下、本問では、数に付された括弧付きの添字は基数を表す。また、丸めが必要な場合は、最近接丸め(偶数)を用いるものとする。

Consider an 8-bit binary floating-point format called FP8, which has the similar representation as IEEE 754 base-2 floating-point numbers. The bit fields of FP8 consist of, from MSB to LSB, a 1-bit sign bit, a 3-bit exponent using a biased representation of 3, and a 4-bit significand with implicit 1. The representation of infinity and denormalized numbers is also defined in the same way as IEEE 754. For example, if the sign bit is 0, the exponent is 7, and the significand is 0, it represents positive infinity. If the exponent is 0, it represents a denormalized number. In the following questions, the subscript in parentheses denotes the base of the number. Additionally, when rounding is necessary, use the round-to-nearest (ties to even) method.

- (a) FP8形式を用いて表された数 00010110 を 10 進数で表わせ。 Express the number 00010110 represented in FP8 format in decimal.

- (b) 数 -3.375<sub>(10)</sub> を表す FP8 のビット列を示せ。

Provide the bit sequence in FP8 format that represents the number -3.375<sub>(10)</sub>.

- (c) FP8 が表現できる数の中で、負の 0 を除いて 0 に最も近い負の数を 10 進数で表わせ。

Express the negative number closest to zero among the numbers representable by FP8, excluding negative zero, in decimal.

- (d) FP8 が表現できる数の中で、無限大を除いた最大の数を 10 進数で表わせ。

Express the largest number among the numbers representable by FP8, excluding infinity, in decimal.

- (2) パイプライン方式の計算機について、以下の問に答えよ。 Answer the following questions about pipelined processors.

- (a) パイプライン処理における制御ハザードとはどのようなことか説明せよ。 Explain what a control hazard is in pipeline processing.

- (b) 分岐命令に対する分岐予測について、以下の3方式を考える。Consider the following three schemes for branch prediction of branch instructions.

- A 分岐が常に不成立だと予測する方式

A scheme that predicts that the branch will always be not taken.

continued on next page 次 頁 へ 続 く B 分岐が常に成立すると予測する方式

A scheme that predicts that the branch will always be taken.

C 分岐が成立するかどうかは、前回その分岐命令が実行されたときの結果と同じであると予測する方式 (分岐命令が最初に実行されたときは不成立と予測する)

A scheme that predicts that whether the branch will be taken or not is the same as the result of the last time the branch instruction was executed. (It predicts that the branch will be not taken the first time the branch instruction is executed.)

いずれの方式においても、予測が正しかった場合にはペナルティはなく、分岐が不成立だと予測し実際には成立した場合は1サイクル、分岐が成立すると予測し実際には不成立であった場合は3サイクルのペナルティが発生するものとする。

ループを制御する分岐があり、この分岐はn回連続して成立し、その後1回だけ成立しないとする (n は非負の整数)。

A、B、Cの3方式について、このループが最初に実行される際に発生する分岐予測のペナルティをnの式で表し、この場合に3方式のいずれが優れるかを示せ。

In either scheme, assume that there is no penalty if the prediction is correct, one cycle is incurred as penalty if the branch is predicted to be not taken and it actually is taken, and three cycles are incurred if the branch is predicted to be taken and it is actually not taken.

Suppose that there is a branch controlling a loop, and this branch is taken n consecutive times and then not taken once (where n is a non-negative integer).

For each of the three schemes A, B, and C, express the penalty for branch prediction incurred when this loop is first executed in terms of n, and indicate which of the three schemes is superior in this case.

(c) (b) で示した3方式以外の分岐予測方式を一つ上げ、その特徴を述べるとともに、(b) と同じループにおいてペナルティを評価せよ。ただし分岐予測の際のペナルティは、(b) において A、B、Cの3方式において仮定したのと同じであるものとする。

Show a branch prediction scheme other than the three schemes shown in (b), describe its characteristics, and evaluate its penalty in the same loop as in (b). Assume that the penalty for branch prediction is the same as that was assumed for the three schemes A, B, and C in (b).

# 京都大学大学院情報学研究科 通信情報システムコース 修士課程入学者選抜試験問題 (2023 年度 10 月期入学・2024 年度 4 月期入学)

Admissions for October 2023 and for April 2024

Entrance Examination for Master's Program

Communications and Computer Engineering Course

Graduate School of Informatics, Kyoto University

2023年8月7日 13:00-16:00

August 07, 2023 13:00 - 16:00

# 専門基礎B

### **Problem Set B**

### 注意 (NOTES)

- 1. 解答開始の合図があるまで中を見てはいけない。

- 2. これは<u>「専門基礎B」</u>の問題用紙で、表紙共に14枚ある。解答開始の合図があった後、枚数を確かめ、 落丁または不鮮明なものがあれば直ちに申し出ること。

- 3. 問題は6問(B-1, B-2, B-3, B-4, B-5, B-6)ある。3問を選択して解答すること。答案用紙の問題番号欄に問題番号を記入すること。

- 4. 解答は問題ごとに答案用紙1枚を使うこと。答案用紙1枚に2問以上の解答もしくは1問の解答を2枚以上の答案用紙に書いた場合は無効にすることがある。なお、必要な場合「裏に続く」と明記した上で 裏面を使用してもよい。

- 5. 答案用紙は3枚綴じたまま使用し、切り離さないこと。

- 6. 答案用紙の綴じ込みがはずれた場合は、直ちに申し出ること。

- 7. 解答は日本語または英語で行うこと。

- 1. Do not open the pages before a call for starting.

- 2. This is the "Problem Set B" in 14 pages including this front cover.

After the call of starting, check all pages are in order and notify proctors (professors) immediately if missing pages or with unclear printings are found.

- 3. Answer 3 of the following 6 questions: B-1, B-2, B-3, B-4, B-5, and B-6. State the Question Numbers you choose on the Answer Sheet.

- 4. Use one sheet for each question. If required, the reverse side may be used, stating "Over" at the end of the page.

Note that in case two or more questions are answered in one sheet or two or more sheets are used for one question, they may be regarded as no answers.

- 5. Do not separate the pages of answer sheets; keep them bound.

- 6. Notify proctors (professors) immediately if the pages are separated for some reason.

- 7. Answer the questions either in Japanese or English.

Japanese version shall be the authorized version; the English translation for reference only.

## 専門基礎B

B-1, B-2, B-3, B-4, B-5, B-6 の6問から3問を選択して解答せよ。

### Problem Set B

Choose and answer 3 questions out of B-1, B-2, B-3, B-4, B-5, and B-6.

# **B-1**

下記のすべての問に答えよ.

Answer all the following questions.

(1) フーリエ変換に関する以下の問に答えよ. ただし, 関数 f(t) のフーリエ変換は次式で定義される.

Answer the following questions related to a Fourier transform. Note that the Fourier transform of a function f(t) is defined in the following.

$$F(\omega) = \int_{-\infty}^{\infty} f(t) e^{-i\omega t} dt$$

$\left(i = \sqrt{-1}\right)$

(a) 次の関数 f(t) のフーリエ変換を求めよ. ただし, a > 0 である. Find the Fourier transform of f(t) defined in the following, where a > 0.

$$f(t) = \begin{cases} a - |t| & (|t| \le a) \\ 0 & (|t| > a) \end{cases}$$

(b) 次の関数 g(t) のフーリエ変換を求めよ. ただし, a>0 である. Find the Fourier transform of g(t) defined in the following, where a>0.

$$g(t) = \left\{ egin{array}{ll} a & (|t| \leq a) \ 2a - |t| & (a < |t| < 2a) \ 0 & (|t| \geq 2a) \end{array}

ight.$$

(2) 次の微分方程式の一般解を求めよ.

Find the general solution of the following differential equation.

$$\frac{\mathrm{d}^2 y}{\mathrm{d}x^2} - \frac{\mathrm{d}y}{\mathrm{d}x} - 2y = 20\cos x$$

(3) 留数定理を用いて、次の積分 I を求めよ.

Evaluate the following integral I by using the residue theorem.

$$I = \int_{-\infty}^{\infty} \frac{e^{ix}}{\cos(ix)} dx \qquad (i = \sqrt{-1})$$

下記のすべての問に答えよ。

Answer all the following questions.

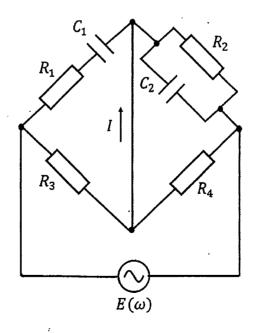

(1) 図  $^{1}$  に示す回路について、以下の問に答えよ。 $\omega$  を交流電源 E の角周波数とし、I を図  $^{1}$  に示した部分を流れる電流とする。

Answer the following questions regarding the circuit shown in Figure 1 .  $\omega$  is the angular frequency of AC power E, and I is the current designated in Figure 1 .

- (a) I=0 となるための平衡条件を求めよ。 Show the balanced condition to be I=0.

- (b)  $C_1$  は真空中に置かれた平行板コンデンサであるとし、端の影響は無視できるものとする。 $C_1$  の極板間隔を 2 倍として比誘電率  $\varepsilon_r$  の誘電体を極板間全体に挿入する。 $R_1$  が可変抵抗である場合、I=0 の平衡条件を保つためには  $R_1$  と  $\omega$  をどのように変化させればよいか。 Assume that  $C_1$  is a parallel-plate capacitor placed in vacuum where the edge effect can be ignored. Double the distance of the parallel plates, then insert a dielectric material with the relative permittivity of  $\varepsilon_r$  to fill the space between the plates of the capacitor  $C_1$ . When  $R_1$  is a variable resistance, show how to modify  $R_1$  and  $\omega$  in order to keep the balanced condition I=0.

- (c) 問 (b) と同様に  $C_1$  を変化させた場合を考える。 $R_1$  と  $R_4$  が可変抵抗である場合、問 (a) の場合と同じ交流電源の角周波数  $\omega$  で I=0 の平衡条件を保つためには  $R_1$  と  $R_4$  をどのように変化させればよいか。

Consider that  $C_1$  is modified in the same way as Question (b). When  $R_1$  and  $R_4$  are variable resistances, show how to modify  $R_1$  and  $R_4$  in order to keep the balanced condition I=0 with the AC power frequency  $\omega$  to be the same as that for Question (a).

図 1 Figure 1

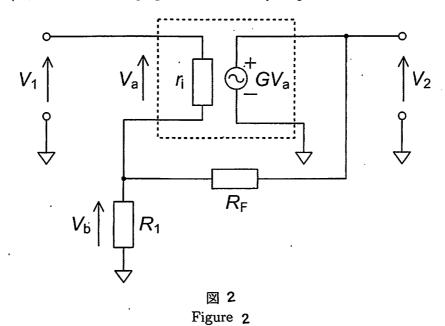

(2) 図  $\bf 2$  は入力インピーダンス  $r_i$ 、電圧増幅度  $\bf G$  の増幅器を用いた回路である。下記の問に答えよ。

Figure 2 shows a circuit with an amplifier with input impedance  $r_i$  and voltage gain G. Answer the following questions.

- (a)  $V_a$ と $V_b$ を求めよ。 Find  $V_a$  and  $V_b$ .

- (b)  $V_2/V_1$  を求めよ。 Find  $V_2/V_1$ .

- (c) 電圧増幅度 G が無限大のときの  $V_2/V_1$  を求めよ。 Find  $V_2/V_1$  when the voltage gain G is infinitely large.

(3) 以下の用語を説明せよ。

Explain the meanings of the terms below.

- (a) 電気回路の有効電力と力率 Effective power and power factor in electrical circuits

- (b) 電気回路のインピーダンス整合 Impedance matching in electrical circuits

- (c) 電磁気学の電界に関するガウスの法則 Gauss' law of electric field in electromagnetism

下記のすべての問に答えよ. (English translation is given on the next page.)

(1) 次に示す直交周波数分割多重 (Orthogonal Frequency-Division Multiplexing, OFDM) 信号に関する以下の問に答えよ.

$$s_m(t) = \sum_{n=0}^{N-1} \left( a_n^m \cos(2\pi n f_0 t) - b_n^m \sin(2\pi n f_0 t) \right)$$

ここで、 $s_m(t)$  は第 m 番目 OFDM シンボルのベースバンド信号、 $f_0$  はサブキャリア間隔、N はサブキャリア数、 $a_n^m + jb_n^m$  は第 m 番目 OFDM シンボルにおける第 n 番目サブキャリアの複素変調シンボルであり、 $a_n^m \in \{-3, -1, 1, 3\}, b_n^m \in \{-3, -1, 1, 3\}$  であるとする.

- (a) 各サブキャリアの変調方式の名称を答えよ.

- (b)  $s_m(t)$  を用いて第 k 番目サブキャリアの  $a_k^m$  と  $b_k^m$  を導出せよ. ただし Cyclic Prefix (CP) 長を含まない OFDM シンボル長(有効シンボル長)は  $T=1/f_0$  である.

- (c) OFDM 方式ではマルチパス遅延に耐性を持たせるため、想定される最大遅延時間以上の長さを もつ CP を各 OFDM シンボルに挿入して伝送する. この CP の挿入によって発生を防ぐこと ができる干渉を 2 つ答えよ.

- (d) 伝搬経路差が最大  $300\,\mathrm{m}$  である  $2\,\mathrm{r}$ ス伝送環境において, $100\,\mathrm{Mbps}$  伝送を行うために必要なサブキャリア数を求めよ.またその理由も説明せよ.ただし,CP 長と有効シンボル長の比率は $1:9\,\mathrm{b}$  とし,フェージングや雑音による信号劣化は考えないものとする.また光速は  $3\times10^8\,\mathrm{m/s}$  とする.

- (2) 最大システム内呼数が 3 であり,サーバ数が 2 である待ち行列 M/M/2/3 システムにおける呼の 到着を考える.  $\lambda$  [呼/秒] と  $\mu$  [呼/秒] は,それぞれ到着率とサービス率である.  $\rho=\frac{\lambda}{\mu}$  とする.システム内の呼数が n である確率を p(n) とする.以下の間に答えよ.

- (a) 状態遷移図を示せ.

- (b) 平衡状態方程式を示せ.

- (c) p(0), p(1), p(2), および, p(3) を  $\rho$  を用いて求めよ.

- (d) 呼が損失する確率(ブロッキング率)を $\rho$ を用いて求めよ.

- (e) システム内平均呼数を  $\rho$  を用いて求めよ.

- (f) 平均システム内滞在時間を  $\rho$  と  $\lambda$  を用いて求めよ.

continued on next page

Answer all the following questions.

(1) Answer the following questions related to the Orthogonal Frequency-Division Multiplexing (OFDM) signal shown below;

$$s_m(t) = \sum_{n=0}^{N-1} \left( a_n^m \cos(2\pi n f_0 t) - b_n^m \sin(2\pi n f_0 t) \right)$$

where  $s_m(t)$  is the baseband signal of the mth OFDM symbol,  $f_0$  is the subcarrier interval, N is the number of subcarriers,  $a_n^m + \mathrm{j} b_n^m$  is the modulated complex symbol of the nth subcarrier of the mth OFDM symbol,  $a_n^m \in \{-3, -1, 1, 3\}$ , and  $b_n^m \in \{-3, -1, 1, 3\}$ .

- (a) Give the name of the modulation scheme for each subcarrier.

- (b) Derive  $a_k^m$  and  $b_k^m$  of the kth subcarrier using  $s_m(t)$ . Here the effective symbol length, which is OFDM symbol length without cyclic prefix (CP), is  $T = 1/f_0$ .

- (c) In the OFDM system, a CP with a length longer than the expected maximum delay time is inserted to each OFDM symbol for transmission to tolerate multipath delays. Answer two interferences that can be prevented by inserting this CP.

- (d) Find the required number of subcarriers for 100 Mbps transmission in a two-path transmission environment where the maximum difference in propagation paths is 300 m with the reason. The ratio of CP length to effective symbol length is 1:9, signal degradation due to fading and noise should not be considered, and the speed of light is assumed to be 3 × 10<sup>8</sup> m/s.

- (2) Consider call arrivals at the M/M/2/3 queuing system, where the maximum number of calls is three and the number of servers is two.  $\lambda$  [calls/second] and  $\mu$  [calls/second] are arrival and service rates, respectively.  $\rho$  is defined as  $\rho = \frac{\lambda}{\mu}$ . p(n) is the probability that the number of calls in the system is n. Answer the following questions.

- (a) Draw the state transition diagram.

- (b) Show the equilibrium state equations.

- (c) Find p(0), p(1), p(2), and p(3) by using  $\rho$ .

- (d) Find the probability that a call is lost, i.e., blocking probability, by using  $\rho$ .

- (e) Find the average number of calls in the system by using  $\rho$ .

- (f) Find the average sojourn time in the system by using  $\rho$  and  $\lambda$ .

下記のすべての問に答えよ。

Answer all the following questions.

(1) 32 ビット語長バイトアドレッシングのマルチサイクルプロセッサ P が、表に示す命令セットを持つものとする。例えば add はレジスタ R[rs] と R[rt] の和をレジスタ R[rd] に書き込む。lw はレジスタ R[rs] に即値を加えたアドレスのメモリから読み出したデータをレジスタ R[rt] に格納する。ただし、R[x] はレジスタ番号 x のレジスタ、M[x] はアドレス x のメモリを表す。また、Imm は即値、SignExtImm は即値を符号拡張した値、BrAddr は SignExtImm を左に 2 ビットシフトした値、PC はプログラムカウンタである。レジスタ R[0] はゼロレジスタであり、その値は常に 0 である。命令長は、オペランドを含めて 32 ビット固定長である。以下の問に答えよ。

Consider a multi-cycle processor P with a 32-bit word length and byte addressing, which has an instruction set shown in the table below. For example, the "add" instruction writes the sum of registers R[rs] and R[rt] to register R[rd]. The "lw" instruction loads the data from the memory address obtained by adding an immediate value to the value in register R[rs], and stores the data in register R[rt]. Here, R[x] represents register x and M[x] represents a memory at address x. Additionally, Imm represents an immediate value, SignExtImm represents a sign-extended immediate value, BrAddr represents the value obtained by left-shifting SignExtImm by 2 bits, and PC is the program counter. Register R[0] is the zero register, and its value is always 0. The instructions are 32 bit fixed length including the operand. Answer the following questions.

| 命令          | アセンブリ・コード / Assembly code                                          |  |  |

|-------------|--------------------------------------------------------------------|--|--|

| Instruction | 動作 / Operation                                                     |  |  |

| . add       | add rd, rs, rt                                                     |  |  |

|             | addition: $R[rd]=R[rs]+R[rt]$ , then $PC=PC+4$                     |  |  |

| sub         | sub rd, rs, rt                                                     |  |  |

|             | subtraction: R[rd]=R[rs]-R[rt], then PC=PC+4                       |  |  |

| beq         | beq rt, rs, Imm                                                    |  |  |

|             | branch if equal: if (R[rs]==R[rt]) PC=PC+4+BrAddr else PC=PC+4     |  |  |

| bne         | bne rt, rs, Imm                                                    |  |  |

|             | branch if not equal: if (R[rs]!=R[rt]) PC=PC+4+BrAddr else PC=PC+4 |  |  |

| addi        | addi rt, rs, Imm                                                   |  |  |

|             | add immediate: R[rt]=R[rs]+SignExtImm, then PC=PC+4                |  |  |

| lw          | lw rt, Imm(rs)                                                     |  |  |

|             | load word: R[rt]=M[R[rs]+SignExtImm], then PC=PC+4                 |  |  |

| sw          | sw rt, Imm(rs)                                                     |  |  |

|             | store word: M[R[rs]+SignExtImm]=R[rt], then PC=PC+4                |  |  |

(a) 下記のコードは、プロセッサ P のアセンブリコードであり、1 から N までの整数の総和( $\sum_{i=1}^{N}i$ )を計算し、指定されたメモリアドレスに結果を格納するプログラムである。N は正の整数であり、プロセッサ P はアドレス 0x3000 から実行を開始する。レジスタ R[1] は N、レジスタ R[2] は結果を格納するメモリアドレスでそれぞれ初期化されている。下記コードの空欄  $\alpha$  から  $\delta$  について命令、レジスタまたは即値を入れてプログラムを完成させよ。

continued on next page 次 頁 へ 続 く The code below is an assembly code for processor P, which calculates the sum of integers from 1 to N (i.e.,  $\sum_{i=1}^{N} i$ ) and stores the result at the specified memory address. N is a positive integer, and processor P starts execution from address 0x3000. The values of registers R[1] and R[2] are initialized to N and the memory address to store the result, respectively. Complete the program by filling in the blanks  $\alpha$  to  $\delta$  with instructions, registers or immediate values.

| Address | Assembly code                                                |

|---------|--------------------------------------------------------------|

| 0x3000  | add R[3], R[0], R[0]                                         |

| 0x3004  | add R[3], R[3], $\alpha$                                     |

| 0x3008  | addi R[1], $\beta$ , $-1$                                    |

| 0x300c  | $\gamma$ R[0], R[1], $\delta$                                |

| 0x3010  | $\overline{\mathrm{sw}} \ \mathrm{R[3]}, \ \mathrm{0(R[2])}$ |

(b) プロセッサ P のステージ構成と各ステージの処理時間が以下のように与えられているとする。 プロセッサ P の最大動作周波数を答えよ。なお、各ステージは 1 サイクルで完了するとする。

Assume the processor P has the following stage configuration and processing times for each stage. Determine the maximum operating frequency of processor P. Assume each stage completes in 1 cycle.

| ステージ / Stage              | 所要時間 / Execution Time [ps] |  |

|---------------------------|----------------------------|--|

| フェッチ / Fetch              | 150                        |  |

| デコード / Decode             | 120                        |  |

| レジスタ読み出し / Register Read  | 180                        |  |

| 実行 / Execution            | 200                        |  |

| メモリアクセス / Memory Access   | 180                        |  |

| レジスタ書き込み / Register Write | 150                        |  |

(c) 問 (a) のコードを実行するのに要するクロックサイクルを N を用いて表わせ。なお、命令によらず 1 命令の実行には 6 サイクル要するとする。

Express the number of clock cycles required to execute the code in Question (a) using N. Assume that each instruction takes 6 cycles to execute, regardless of the instruction.

| con | tinued | on  | next | page |

|-----|--------|-----|------|------|

| 次   | 頁      | , 🖎 | 続    | <    |

(2) 32 ビット語長、バイトアドレッシングのプロセッサにおいて、32 ビット整数を要素とするサイズ  $64\times 64$  の行列 mat の要素の総和を求める C 言語プログラムの一部 Code segment A または Code segment B を実行する。コンパイラによる最適化は行わず、行列要素数と等しい回数、加算命令が順次実行される。行列要素 mat [i] [j] は、主記憶アドレス  $0x001000000+4\times(64\times i+j)$  に置かれている。

それぞれの間において、プログラム実行前にキャッシュメモリは空である。主記憶は十分に大きく、また主記憶へのアクセスは Code segment A または Code segment B のいずれかにおける行列要素のみであり、他の変数はレジスタ上にあるとする。また、命令キャッシュとデータキャッシュは分離されている。

次の問に答えよ。計算の過程も示すこと。

A 32-bit word-length, byte-addressing processor executes either of the C program code segments, shown in Code segment A or Code segment B, to find the sum of the elements of a matrix mat with a size of  $64 \times 64$ , whose elements are 32-bit integers. No compiler optimization is performed, and the add instructions are executed sequentially for the number of times equal to the matrix element count. The matrix element mat[i][j] is located at the main memory address  $0 \times 00100000 + 4 \times (64 \times i + j)$ .

In each question, the cache memory is initially empty. The main memory is sufficiently large and is accessed only by the matrix elements in Code segment A or Code segment B, and the other variables are placed in registers. The instruction cache and data cache are separated.

Answer the following questions. Also, show the process of calculation.

Code segment A

```

sum = 0;

for (i = 0; i < 64; i++)

for (j = 0; j < 64; j++)

sum += mat[i][j];

sum = 0;

for (j = 0; j < 64; j++)

for (i = 0; i < 64; i++)

sum += mat[i][j];</pre>

```

(a) データキャッシュは、ブロックサイズ 4 語、データ容量 8 Ki バイトのダイレクト・マップ・キャッシュであるとする。Code segment A, Code segment B それぞれについてキャッシュヒット率を求めよ。

Assume that the data cache is a direct map cache with a block size of 4 words and a data capacity of 8 Ki bytes. Find the cache hit ratios for Code segment A and Code segment B.

Code segment B

(b) データキャッシュは、ブロックサイズ 4 語、データ容量 16 Ki バイト、LRU 置き換えの 8 ウェイ・セット・アソシアティブキャッシュであるとする。Code segment A, Code segment B それぞれについてキャッシュヒット率を求めよ。

Assume that the data cache is an 8-way set-associative cache with a block size of 4 words and a data capacity of 16 Ki bytes and that the replacement policy is LRU. Find the cache hit ratios for Code segment A and Code segment B.

以下のすべての問に答えよ。 Answer all the following questions.

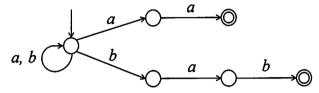

(1) 以下の状態遷移図で表された非決定性有限オートマトン (NFA) により受理される 言語を L とする。以下の問 (a)(b)(c)(d) に答えよ。

Let L be the language accepted by the non-deterministic finite automaton (NFA) with the following state transition diagram. Answer the following questions (a), (b), (c), and (d).

- (a) 文字列 aaaa, baba, abaa それぞれについて、L に含まれるかどうかを答えよ。 Determine whether L includes each of the strings aaaa, baba, and abaa.

- (b) L を認識する決定性有限オートマトン (DFA) の状態遷移図を示せ。状態数は最小とせよ。

Draw the state transition diagram of a deterministic finite automaton (DFA) that recognizes L and that has the minimum number of states.

- (c) Lを表す正規表現を示せ。できるだけ簡潔に表現せよ。

Describe a regular expression that represents L and that is as simple as possible.

- (d) L を生成する正規文法を示せ。できるだけ簡潔な文法とせよ。

Describe a regular grammar that generates L and that is as simple as possible.

- (2) 言語  $L_1, L_2, L_3, L_4$  を以下の通り定義する。

Let  $L_1, L_2, L_3$ , and  $L_4$  be the languages defined as follows.

$\begin{array}{l} L_1 = \{ a^n a^n b^m \mid n \in \mathbb{N}, m \in \mathbb{N} \}, \\ L_2 = \{ a^n b^n b^m \mid n \in \mathbb{N}, m \in \mathbb{N} \}, \\ L_3 = \{ a^n b^m c^n \mid n \in \mathbb{N}, m \in \mathbb{N} \}, \\ L_4 = \{ a^n b^n c^n \mid n \in \mathbb{N} \}, \end{array}$

ただし、 $a^n$  は文字 a が n 個連続することを意味する。以下の問 (a)(b)(c) に答えよ。 Here  $a^n$  means that the letter a runs n times. Answer the following questions (a), (b), and (c).

- (a)  $L_2$  に含まれるが  $L_1$  に含まれない文字列を 1 つ挙げよ。 Show a string which is included in  $L_2$  but not in  $L_1$ .

- (b)  $L_1, L_2, L_3, L_4$  がそれぞれ文脈自由言語に属するか否かを答えよ。(証明はしなくてよい。)

Determine whether each of  $L_1, L_2, L_3$ , and  $L_4$  is a context-free language or not. (No need to prove.)

(c)  $L_1, L_2, L_3, L_4$  がそれぞれ正規言語に属するか否かを答えよ。(証明はしなくてよい。)

Determine whether each of  $L_1, L_2, L_3$ , and  $L_4$  is a regular language or not. (No need to prove.)

continued on next page 次 頁 へ 続 く (3) 以下の問(a)(b) に答えよ。

Answer the following questions (a) and (b).

- (a) 決定不能な問題の定義を述べよ。 Describe a definition of the undecidable problems.

- (b) チューリングマシンの停止性問題について、何を入力として何を出力する問題 であるかを説明せよ。

For the halting problem of Turing machine, explain what is the input and what is the output of the problem.

(4) 以下の問(a)(b) に答えよ。

Answer the following questions (a) and (b).

- (a) 計算量クラス NP, NP 困難, NP 完全の定義を述べよ。 Describe definitions of complexity classes: NP, NP-hard, and NP-complete.

- (b) もしも NP  $\neq$  co-NP が証明されたならば、P  $\neq$  NP もまた証明できるという。この命題が成り立つ理由を説明せよ。 If NP  $\neq$  co-NP has been proved, then P  $\neq$  NP can also be proved. Explain the reason why this proposition stands.

以下の問に答えよ. (English translation is given on the next page.)

文脈自由文法 G は,終端記号の集合  $\Sigma := \{p, \land, \lor, \neg, (,)\}$ ,非終端記号の集合  $N := \{S, E\}$  を持ち,開始記号は S である.また,この文法は  $\land, \lor, \neg$  と原子命題を表す記号 p とからなる(古典)命題論理式を導出する以下の書き換え規則を持つ.

$$S \rightarrow E \quad E \rightarrow E \wedge E \quad E \rightarrow E \vee E \quad E \rightarrow \neg E$$

$$E \rightarrow p \quad E \rightarrow (E)$$

以下の問いに答えよ.

- (1)  $p \wedge (\neg p)$  はこの文法が生成する言語に属するか、属するならば、この終端記号列の導出木を与えよ、属さないならば「属さない」と書け、

- (2) この文法が曖昧であることを,異なる複数の導出木を持つような終端記号列を与えることによって示せ.

- (3) 文法 G は LL(1) 文法か. 理由とともに答えよ.

- (4) G と同じ言語を導出する,曖昧でない文脈自由文法 G' を与えよ.ただし, $\neg$  は  $\land$  より結合が強く, $\land$  は  $\lor$  より結合が強く, $\land$  と  $\lor$  はどちらも左結合となるようにすること.

- (5) 文法が G で与えられる命題論理式を操作する言語処理系を実装したい. 以下の間に答えよ. 解答に 先立ち, 使用するプログラミング言語を以下から一つ選択し明示すること: C, C++, Java, Python, Scheme, Racket, OCaml, Haskell.

- (5-1) 具象構文が G で与えられる命題論理式の抽象構文を Backus-Naur form (BNF) で与えよ.

- (5-2) 問 (5-1) で与えた抽象構文による抽象構文木のデータ構造をあなたの選択したプログラミング言語で設計し、命題論理式  $\neg(p \land (\neg p))$  がそのデータ構造でどのように表現されるかを説明せよ.

- (5-3) 命題論理式は否定記号 ¬ が原子命題のみにかかっているときに否定標準形 (negation normal form; NNF) という. 例えば、命題論理式  $(\neg p) \lor p$  は  $\neg (p \land (\neg p))$  に意味論的に等価な NNF の命題論理式である.  $\neg ((\neg p) \lor ((\neg p) \land p))$  と意味論的に等価な NNF の命題論理式を与えよ.

- (5-4) 命題論理式 e を受け取り、e と意味論的に等価な NNF の命題論理式を返すプログラムを書け.

continued on next page 次 頁。へ 続 く Answer all the following questions.

Consider a context-free grammar G with the set of terminal symbols  $\Sigma := \{p, \land, \lor, \neg, (,)\}$  and the set of non-terminal symbols  $N := \{S, E\}$ . Suppose that the start symbol of G is S. The grammar G has the following rules that derive the formulas of the (classical) propositional logic that consists of the symbols representing an atomic formula p and the operators  $\land, \lor$  and  $\neg$ :

Answer the following questions.

- (1) Does  $p \wedge (\neg p)$  belong to the language that is generated by this grammar? If so, give its derivation tree. If not, write "Does not belong".

- (2) Show that the grammar G is ambiguous by showing a sequence of terminal symbols that can be derived by multiple derivation trees.

- (3) Is G an LL(1) grammar? Answer with an explanation.

- (4) Give a context-free grammar G' that is unambiguous and whose language is the same as that of G. The grammar G' must satisfy the following conditions: (i) ¬ has higher precedence than ∧ and ∧ has higher precedence than ∨; (ii) ∧ and ∨ are both left-associative operators.

- (5) We would like to implement a program that manipulates the propositional formulas whose syntax is given by G. Answer the following questions. Before answering the following questions, declare one programming language that you use from the following choices: C, C++, Java, Python, Scheme, Racket, OCaml, Haskell.

- (5-1) Write a Backus-Naur form (BNF) that describes an abstract syntax of the propositional logic whose concrete syntax is given by G.

- (5-2) Design a data structure for the abstract syntax trees (AST) with the programming language of your choice. Explain how the formula  $\neg(p \land (\neg p))$  is expressed by your data structure. The AST must be based on the abstract syntax defined in question (5-1).

- (5-3) A propositional formula f is called to be in a negation-normal form (NNF) if each occurrence of the negation symbol  $\neg$  in f takes an atomic formula as an argument. For example, a propositional formula  $(\neg p) \lor p$  is an NNF formula that is semantically equivalent to  $\neg(p \land (\neg p))$ . Give an NNF propositional formula that is semantically equivalent to  $\neg((\neg p) \lor ((\neg p) \land p))$ .

- (5-4) Write a program that takes a propositional formula e as input and returns an NNF propositional formula that is semantically equivalent to e.